今年のWWDCではMac Proが登場し、それまでにすべてのMacがApple Siliconに置き換わると見られていることからWWDC 20から始まったMacのプロセッサ置き換え計画は幕引きとなり、Apple Siliconのみで展開されるMacラインナップが完成することになる。今回はMac ProのSoCの話である。

先日の記事でMac ProのSoCの話を別ですると言ったのでこの記事でします。文章の構成上今回はだ・である口調です。許して

記事の執筆上、高性能コアと高効率コアの呼び方をIntelのものに統一し、高性能コアを「Pコア」、高効率コアを「Eコア」と呼ぶことにします(正式には高性能コアと高効率コアです)。

Mac Pro SoC

Mac Proが搭載するSoCは40コアCPUを搭載し、128コアGPUを搭載すると言われている。40コアCPUのPコアとEコアの比率は一切明らかになっていませんので憶測に基づく。

パッケージ・ダイ

まず、40C 128Gというコア数は、MacBook Pro 14"/16"に搭載されるApple M1 Maxのちょうど4倍のコア数だ。つまり、この話が正しければ、Mac Proに採用されるSoCは以下の2つどちらかのダイになる。

- M1アーキテクチャ(Fire Storm&Ice Storm)を40C 128GまでスケールさせたSoC(モノリシックダイ)

- M1 Maxを4つ内蔵したSoC(マルチダイ)

モノリシックダイ

モノリシックダイになった場合、40コアCPUの内訳はわからない。40コアすべてがPコアになるかもしれないし、これまでにない比率(例えばP 36: E4)で搭載される可能性もある。

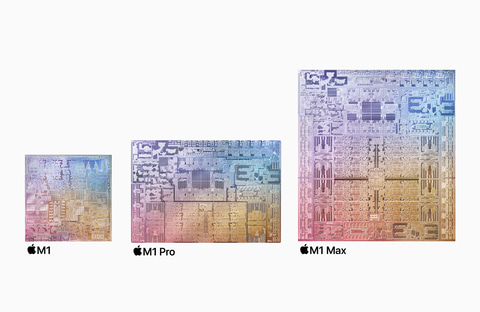

こちらはAppleが発表会で用いたApple M1シリーズのチップサイズの比較だ。この比率が正しいということを前提にして、この画像をもとに実際に比べてみるとM1 MaxはM1の4倍よりやや小さめ。

実際にダイサイズに影響するトランジスタ数を比較すると、M1が160億、M1 Proが337億、M1 Maxが530億となり、M1 MaxはM1に比べて3.5倍多いトランジスタを搭載している。実際にトランジスタ数が3.5倍になったからサイズも正確に3.5倍になるというわけではないが、おおよそ3.5倍程度に収まっている。

もしも、Mac Pro向けSoCがこれをSoC全体で4倍にスケールしたならばダイサイズも4倍、トランジスタ数も4倍になることになりますが実際にはそうはならない。

理由はApple SiliconはCPU・GPUだけでなく、数あるコントローラやアクセラレータ、エンジンを一つのチップにまとめており、それらすべてを4倍にしたところでそれらの性能も4倍になるわけではないためだ。例えばCPU/GPUなどをメモリにつなぐときのファブリックは4つあるのはちょっと意味がわからない

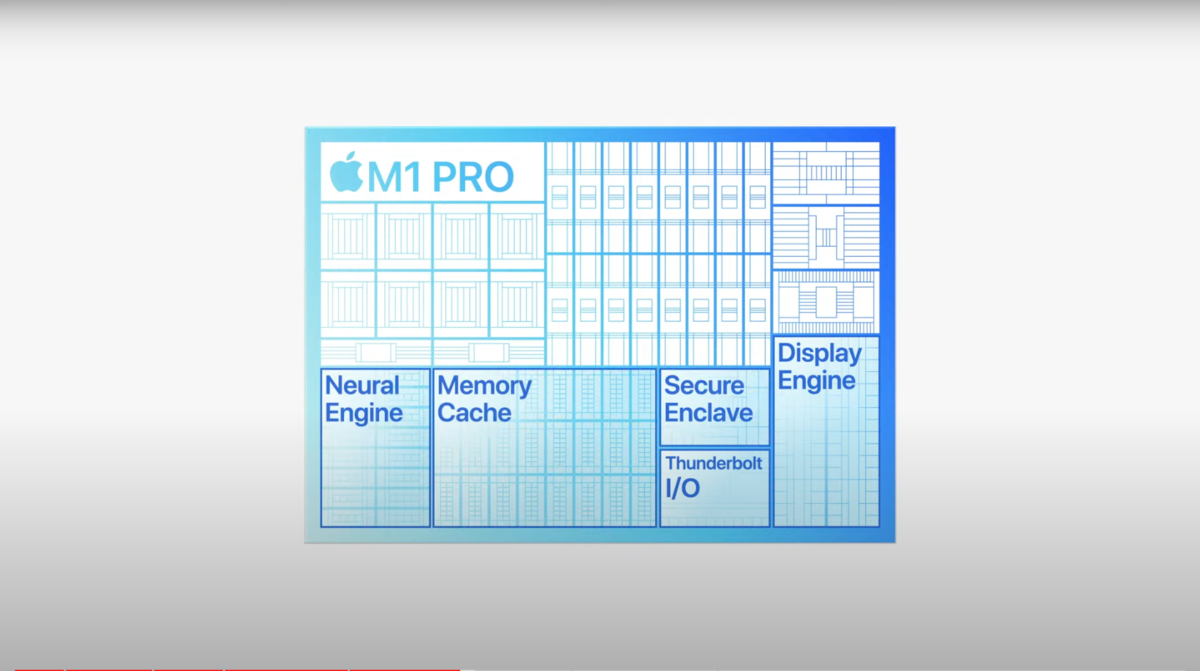

M1 Maxでは同様の図が示されなかったのでM1 Proで代用するが、M1とM1 Pro、M1 Maxは規模が違うにも関わらずニューラルエンジンなどのコア数はどれも同じ数搭載されている。さすがにコントローラはM1とM1 Pro/Maxで差があるが、M1 ProとM1 Maxの間では差はない。ということから考えると、Mac Proのトランジスタの増加率もおおよそM1 Maxの3.5倍、約2000億基になることが想定される。

もし2000基ものトランジスタがモノリシックダイに搭載されるとするとダイサイズはとてつもなく大きくなることになる。

基本的にダイサイズが大きいことにメリットというのはあるものの、製造過程から見るとデメリットが深刻だ。

まず、ダイサイズが大きいことによって、ウェハから切り出せる量が減る。M1 Max比3.5倍と考えると、同じサイズのウェハから切り出せるSoCの数は0.28倍となる。ただしこの欠点から生じる「ダイの生産量が減る」という問題点は、そもそもMac Pro自体需要がさほど高くないので目立ちにくく、かつウェハサイズを大きくすればなんとかなるうえ、「コスト」についてはMac Proそもそも値段高いから問題ないだろう。

本当に問題なのは歩留まりだ。わかりやすく説明すると、大きければ大きいほど、完全なダイが製造しにくいということである。基本的にウェハから切り出されたダイは欠損していたら使えそうなら下位モデルに回される。この例はM1でGPUが1基無効になったものがあるがあれはGPUが欠損してしまった個体であると考えられる。おそらく、Mac ProのSoCも複数のバリエーションが用意され、40コアCPU 128コアGPUを作ろうとした欠損品が下位のバリアントに採用されることになるだろう。

しかし、そもそも最上位グレードがある時点で完全な個体が必要なのも事実である。歩留まりがどれくらいのものかわからないが、もしかしたらそんな個体がウェハ1枚から1つ切り出せたらいい方かもしれない。

このことを考えるとMac ProのSoCがモノリシックダイであるとは正直考えにくい。

マルチダイ

もう一つがマルチダイであるという可能性だ。これはいわゆるマルチダイとかそういうやつである。

IntelやAMDがいうマルチダイというのは基本的に各機構ごとにダイ(チップレット)を分散する方式である。例えばAMDのデスクトップ向けRyzen APUでは、CPUダイとGPUダイ、IOダイという3つのチップレットが一つにパッケージされている。一つのダイが2つ以上の機能を持ってはいない。

AppleがこのCPUとGPUを分離したパッケージにすることは考えられなくもないが、実際には多分統合グラフィックとUMAを推進しているためAMDやIntelのようなCPUとGPUが個別の方式は考えにくい。ではどのようなマルチダイになると予想しているかというと、M1 Maxを4つ搭載したパッケージである。

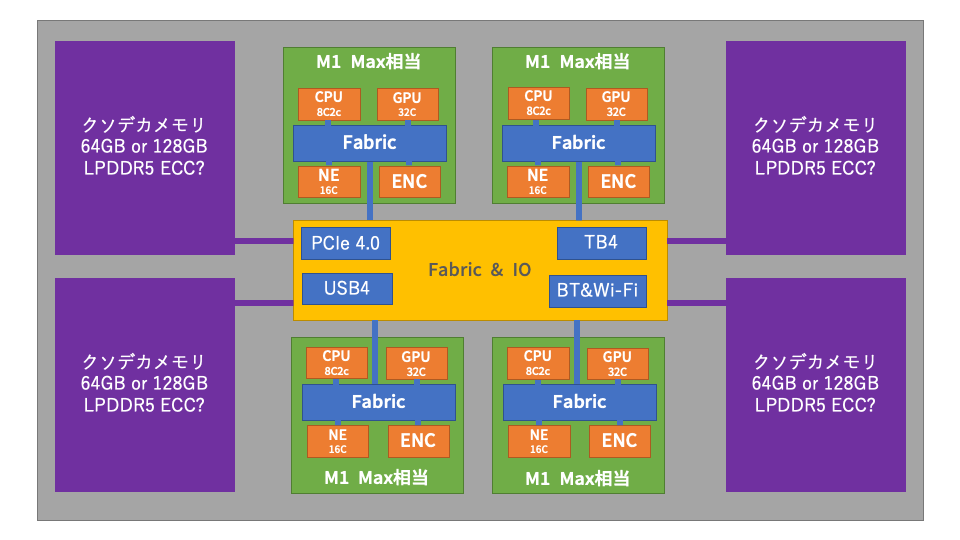

これは、私が予想しているパッケージである。モノリシックダイではCPU・GPU以外の機構は4倍されないなんて言ったが、この形式になった場合、SoCすべてが4倍されるのでニューラルエンジンも64コアになる。ファブリックは最大5つに増え、各SoC内のファブリックとそれを束ねるファブリックになるだろう。

そして、各種コントローラは各SoCを束ねるファブリックに集約されると見られる。

この形式をとった場合、トランジスタ数はM1 Maxの4倍以上になることは間違いなく、少なくとも2300億は下らないことにはなるだろうが、歩留まりはかなり良くなる。理由は、M1 Maxを作っているだけだからである。もっと簡潔に言うと、MacBook Pro 4台分のSoCを作ってそれをパッケージするだけ。無論M1 Max自体もそれなりに高価なのでMac ProのSoCも高価になるだろうが、そもそもMac Proに採用されていたXeonプロセッサは100万を下らないバリエーションも普通にあるので大した問題ではない。

ただし、これにももちろんデメリットがある。まず、管理の仕方がマルチプロセッサというよりかはマルチシステムに近い状態になることだ。基本的にIntelやAMDのチップレットという言葉自体はCCDのようなCPUならCPU、GPUならGPUの機能のみを持つものを意味する。この考え方はAppleが推し進めるSoCとは真反対の考え方である。

そもそもSoCは、System on Chipの略である。英語の文法的な話をすると、on ChipはあくまでSystem を修飾しているための補語なので、SoC=システムである。これはつまりSoCだけでシステムが完結することを意味している。XeonやEPYCの2-wayのようなマルチプロセッサはそれだけでは動かず、GPUやメモリを用意する必要があるが、SoCはそれだけで動作することができる。つまり、Mac Proのパッケージは最大4つのシステムが同時に並行して動作しているということになる。

もっと簡単に言うと、この構成でMac Proが稼働すると、Mac Proの中で4つの(MacBook Proの性能を持つ)コンピュータが動いているということである。ちょっと専門的な話なので間違っている可能性があるが、SoCとしてMac Proのプロセッサが構成されるならば、対称型マルチプロセッサ(SMP 高性能コア間の処理)と非対称型マルチプロセッサ(ASMP ハイブリッドシステム)が混ざりあったシステムになることだろう。

そして、SoC間の通信も気になる。例えば、CPUではなくGPUだが、現行のMac Proの最上位 Radeon PRO W6800X Duoは一つのカードに2つのGPUがありそれを一つのクラスタとして、その間の通信をInfinity Fabricで行っているがその帯域は84GB/sで通信する。GPUのみの場合、GPU間のファブリック(NVLinkとかInfinity Fabricとか)が使われるし、CPUの場合メモリベースになるが、SoCの場合はどうなるのだろうか。多分これはUMAを使うことになる。

メモリ

UMAはユニファイドメモリアーキテクチャの略で、Apple Siliconのメモリ方式である。これは、メインメモリとビデオメモリを統一し、各機構のメモリをすべて同じにすればわざわざCPU・GPU間のインターフェイスも不要だしレイテンシも少なくてすむよねっていう話である。おそらくMac ProもUMAをベースにするはずだ。

マルチダイを採用した場合、おそらく各SoCは同じUMAにアクセスすることになる。

現在、M1 Maxは512bitインターフェイスのLPDDR5メモリを採用している。これで帯域は400GB/sを実現しており、正直SoC間の通信はこれで十分な気がするが、個人的にはAppleがHBM2やHBM2eメモリを採用することもありえなくはないと思っている。もしそうなれば、帯域は1TB/s程度まで上がり、HBM2eなら1.5TB/sも夢じゃない。かつAppleも「統合」をある程度維持できる。

個人的に割と当たってると思う。

インターフェイスと外部GPU

Mac Pro 2019で復活したPCIe レーンやメモリアクセスだが、私の意見として両方ともアクセスできないようになると考えている。まず、メモリについてはUMAが採用されればパッケージにはんだ付けであり、ユーザーでの換装はかなりこんなんだろう。PCIeについては、M1自体特殊なので対応パーツがあるかがかなり怪しい。そもそもDDR4やDDR5ならDIMMがあるが、マルチダイ方式の場合、Appleは帯域の問題上LPDDR5かHBMを採用すると見られる。モノリシックダイでDDRだとしてもAppleからすればM1 Maxよりも帯域が低いDIMMを採用するとは思えない。

少なくとも統合GPU以外の外部GPUはApple Silicon自体が受け付けない可能性がある。理由は現行のApple Silicon MacがすべてeGPUをサポートしていないからだ。多分これは、Appleが求める帯域をPCIeが実現出来ないからだとおもう(あるいは技術的な問題?)。そもそも、次期Mac Pro自体が小型化するという話がある時点で、PCIeのアクセスは考えにくい。正直これについては、今後の対応に期待したい(個人的にApple GPU搭載MPX Moduleとか出てきてくれたら面白いのになって思っている)。

SSD

もし、Mac Proでアクセスができるとすれば残るはSSDだ。現行のMac ProもSSDの換装はできる。

SoCに関係ない唯一の部分なのでここだけは期待したい。

締め

今回の話は個人的な憶測に基づくものであるが、割と当たってると思う。ただし何の根拠もないわけだが。

Mac Proは遅くても今年のWWDCで必ず登場するはずなので、あと半年楽しみに待つことにしよう。